NMOS and PMOS Logic

a. Mengetahui pengertian NMOS dan PMOS

b. Mengetahui logika NMOS dan PMOS

1. Mosfet-N

Struktur N-Channel Mosfet atau disebut dengan NMOS terdiri dari subtract tipe P dengan daerah Source dan Drain deberi Difusi N+. Diantara daerah Source dan Drain terdapat sebuah celah sempit dari subtract P yang di sebut dengan channel yang di tutupi oleh isolator yang terbuat dari Si02

2. Mosfet-P

P-Channel MOSFET memiliki wilayah P-Channel diantara Source dan Drain. Dia memiliki empat terminal seperti Gate, Drain, Source dan Body. Struktur Transistor PMOS terdiri atas tipe-n dengan daerah Source dan Drain diberi difusi P+.

3. VCC dan Ground

Ground berfungsi sebagai acuan dan sebagai arah tujuan arus mengalir dikarenakan arus mngalir dari potensial tinggi kepotensial rendah.

4. Logicstate dan Logicprobe

Logicstate berfungsi sebagai pemisalan untuk input/masukan sedangkan logicprobe berfungsi sebagai indikator output dengan pemisalan '1' adanya tegangan dan pemisalan '0' tidak adanya tegangan

Logika PMOS

Keluarga logika PMOS menggunakan MOSFET P-channel. Gambar (a) menunjukkan rangkaian inverter menggunakan logika PMOS. MOSFET Q 1 bertindak sebagai beban aktif untuk sakelar MOSFET Q 2 . Untuk sirkuit yang ditunjukkan, GND dan −V DD masing-masing mewakili logika '1' dan logika '0' untuk sistem logika positif. Ketika input di-ground (yaitu logika '1'), Q 2 tetap dalam cut-off dan DDV DD muncul pada output melalui Q 1 yang melakukan. Ketika input berada pada −V DD atau dekat −V DD , Q 2 melakukan dan output mendekati potensial mendekati nol (yaitu logika '1'). Gambar (b) menunjukkan logika PMOS berbasis dua input gerbang NOR . Dalam susunan logika dari Gambar (b), keluaran menuju ke keadaan logika '1' (yaitu potensial tanah) hanya ketika Q1 dan Q2 melakukan.

Dapat disebutkan di sini bahwa MOSFET yang digunakan sebagai beban [Q1 pada Gambar (a) dan Q3 pada Gambar (b)] dirancang sedemikian rupa sehingga memiliki ketahanan terhadap- ON yang jauh lebih besar daripada total ON- resistensi MOSFET yang digunakan sebagai sakelar [Q 2 pada Gambar. (a) dan Q 1 dan Q 2 pada Gambar. (b)].

Logika NMOS

Keluarga logika NMOS menggunakan MOSFET N-channel. Perangkat MOS N-channel membutuhkan area chip yang lebih kecil per transistor dibandingkan dengan perangkat P-channel, dengan hasil bahwa logika NMOS menawarkan kepadatan yang lebih tinggi. Juga, karena mobilitas pembawa muatan yang lebih besar di perangkat saluran-N, keluarga logika NMOS juga menawarkan kecepatan yang lebih tinggi.

Karena alasan inilah sebagian besar perangkat memori MOS dan mikroprosesor menggunakan logika NMOS atau beberapa variasi seperti VMOS, DMOS dan HMOS. VMOS, DMOS dan HMOS hanyalah variasi struktural dari NMOS, yang bertujuan untuk lebih mengurangi penundaan propagasi. Angka (a), (b) dan (c) masing-masing menunjukkan inverter, dua input NOR dan dua input NAND menggunakan logika NMOS . Sirkuit logika cukup jelas.

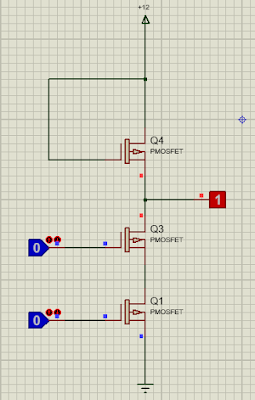

Gambar 4.1 Rangkaian Logika PMOS Inverter dan Logic NOR

Gambar 4.2 Rangkain Logika NOR

Prinsip Kerja

Gambar (4.1) adalah gambar rangkaian PMOS Logic inverter yang mana nilai masukannya akan dibalikkan dinilai outputnya.

Pada Gambar (4.2) merupakan Rangkaian PMOS dengan logika NOR yang mana Output akan berlogika '1' ketika kedua input berlogika '0'

Logika NMOS

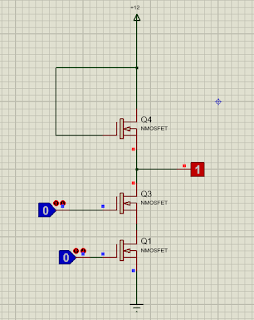

Gambar 4.3 rangkaian NMOS logic Inverter

Gambar 4.4 NMOS Logic dua input

Prinsip Kerja

Gambar (4.3) adalah gambar rangkaian NMOS logic Inverter yang nilai Inputnya akan dibalikkan dinilai keluarannya.

Pada Gambar (4.4) adalah gambar rangkaian logika NMOS dengan dua input yang mana akan berlogika '1' ketika nilai vdd= +v dan berlogika '0' ketika vdd= -v

Video rangkain 3 dan 4

Download file rangkaian :

rangkaian 1 disini

rangkaian 2 disini

rangkaian 3 disini

rangkaian 4 disini

Download Datasheet disini

rangkaian 1 disini

rangkaian 2 disini

rangkaian 3 disini

rangkaian 4 disini

Download Datasheet disini

Download HTML disini

Tidak ada komentar:

Posting Komentar