R-S Flip-Flop

- Mengetahui pengertian R-S Flip-Flop

- Mengetahui logika R-S Flip-Flop

- Dapat merangkai rangkaian dalam R-S Flip-Flop

1. Gerbang NAND

2. NOR

Arti NAND adalah NOT AND atau BUKAN AND, Gerbang NAND merupakan kombinasi dari Gerbang AND dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang AND.

Arti NOR adalah NOT OR atau BUKAN OR, Gerbang NOR merupakan kombinasi dari Gerbang OR dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang OR.

3. Logic Probe

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan

mengecek status logika (High atau Low) yang keluar dari rangkaian digital. Objek yang diukur

oleh logic probe ini adalah tegangan oleh karena itu biasanya rangkaian logic probe harus

menggunakan tegangan luar (bukan dari rangkaian logika yang ingin diukur) seperti baterai. Alat

ini biasa digunakan pada IC TTL ataupun CMOS (Complementary metal-oxide semiconductor).

4. Logicstate

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan

mengecek status logika (High atau Low) yang keluar dari rangkaian digital. Objek yang diukur

oleh logic probe ini adalah tegangan oleh karena itu biasanya rangkaian logic probe harus

menggunakan tegangan luar (bukan dari rangkaian logika yang ingin diukur) seperti baterai. Alat

ini biasa digunakan pada IC TTL ataupun CMOS (Complementary metal-oxide semiconductor).

4. Logicstate

logicstate memiliki 2 kode simbol yaitu 0 dan 1. apabila logicstate melambangkan 1 maka akan ada tegangan yang mengalir sedangkan 0 tidak ada tegangan yang mengalir.

5. Clock

Clock merupakan sinyal listrik yang berupa suatu denyutan dan berfungsi untuk mengkoordinasikan atau mengsinkronisasikan setiap aksi2x atau proses2x yg dilakukan oleh setiap komponen didalam perangkat elektronika.

6. Gerbang NOT

Gerbang NOT sering juga disebut sebagai rangkaian inventer (pembalik). Tugas rangkaian NOT (pembalik) ialah memberikan suatu keluaran yang tidak sama dengan masukan.

Flip-flop adalah susunan gerbang logika yang menjaga keluaran tetap sta-bil walaupun masukan sudah tidak aktif. Keluaran flip-flop ditentukan oleh nilai masukan dan juga nilai keluaran sebelumnya, sehingga unit logika kom-binasional tidak cukup untuk menangani hal ini. Flip-flop dapat digunakan untuk menyimpan informasi bit tunggal, dan berlaku sebagai pembangun memori komputer.

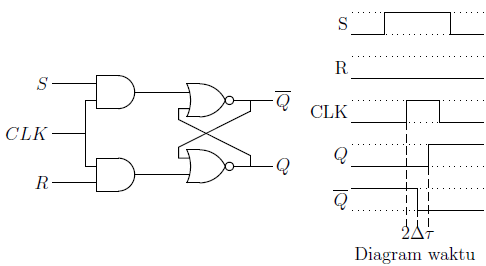

Ada banyak cara untuk menyusun rangkaian sebuah flip-flop S-R. Penggunaan gerbang NOR yang saling silang untuk flip-flop S-R adalah hanya salah satu cara. Dua gerbang NAND yang dihubungkan saling silang juga dapat menghasilkan flip-flop S-R, dengan nilai S = R = 1 mengakibatkan keluaran tidak berubah. Dengan menggunakan teorema DeMorgan kita dapat mengubah gerbang NOR dalam flip-flop S-R menjadi gerbang AND seperti dalam Gambar 4.4. Dengan penggeseran gelembung, maka gerbang AND dapat diubah menjadi gerbang NAND. Penggeseran gelembung pada S dan R mengakibatkan pertukaran label S dan R.

Gambar 4.4: Flip-flop S-R dengan NAND

SR Flip-Flop Berdetak

Perlu diketahui bahwa masukan ke flip-flop S-R dapat berasal dari keluaran rangkaian lain, dalam bentuk rangkaian logika berjenjang. Hal ini biasa terjadi pada rangkaian logika konvensional. Masalahnya adalah transisi dapat terjadi pada waktu yang tidak diinginkan.

Perhatikan rangkaian pada Gambar 4.5. Jika sinyal A,B, dan C semuanya berubah dari keadaan 0 menjadi 1, maka sinyal C akan mencapai gerbang XOR sebelum A dan B keluar dari gerbang AND. Akibatnya nilai S akan 1 walaupun sebentar sampai keluaran dari gerbang AND sudah mantap dan dioperasian XOR dengan C. Jika nilai 1 pada S bertahan cukup lama maka akan mengakibatkan nilai yang tersimpan dalam flip-flop bisa berubah.

Gambar 4.5 Rangkaian yang mengandung hazard

Jika keadaan akhir dari flip-flop sensitif terhadap kedatangan sinyal maka dapat menimbulkan glitch, yang sebenarnya merupakan keadaan atau keluran yang tidak diinginkan. Rangkaian yang dapat menghasilkan glitch disebut rangkaian yang mengandung hazard.

Untuk menyelaraskan pengendalian terhadap rangkaian yang tergantung pada keadaan (misalnya flip-flop) maka digunakanlah detak (clock) yang akan mengaktifkan rangkaian dalam selang waktu tertentu secara serentak. Rangkaian detak menghasilkan sinyal 1 dan 0 bergantian terus menerus dengan periode waktu yang tetap sehingga membentuk gelombang kotak seperti Gambar 4.6. Waktu yang diperlukan detak untuk naik, turun dan kemudian mulai naik lagi disebut waktu siklus atau periode. Gelombang kotak yang ditampilkan pada gambar tersebut adalah bentuk gelombang detak ideal. Dalam kenyataannya, gelombang tersebut tidak berbentuk persegi tetapi membulat karena perlu waktu untuk menjadi tinggi dan rendah, tidak berlangsung seketika.

Gambar 4.6 Detak yang berupa gelombang kotak

Kecepatan detak berkebalikan dengan waktu siklus. Untuk waktu siklus sebesar 25 ns/siklus berarti kecepatannya adalah 1/25 siklus/ns, yang sama dengan 40.000.000 siklus per detik atau 40 MHz.

Kita dapat menggunakan sinyal detak untuk menghilangkan hazard dengan membuat flip-flop S-R berdetak, yang dapat dilihat pada Gambar 4.7. Simbol CLK berarti clock atau detak. Sekarang S dan R tidak dapat mengubah keadaan hingga detak bernilai tinggi. Dengan demikian S dan R dibuat mantap dahulu pada posisi detak rendah, baru kemudian detak menjadi tinggi dan nilai yang stabil akan tersimpan dalam flip-flop.

Gambar 4.7 Flip-flop S-R berdetaka

1. R-S Flip-Flop with Active LOW Input

Prinsip kerja rangkaian diatas ketika S berlogika 0 (a) dan berlogika 0 (b), gerbang NAND 1 akan berlogika 1 karna pada bagian (y) gerbang NAND merupakan not (y). ketika R berlogika 1 (a) dan berlogika 1 (b) , gerbang NAND 2 akan berlogika 0 karena pada bagian (y) gerbang NAND merupakan not (y).

Berikut tabel kebenarannya

Tabel Kebenaran R-S Flip-Flop with Active LOW Inputs

2. R-S Flip-Flop with Active HIGH Inputs

Gambar (b) 10.18 R-S flip-flop with active HIGH inputs

Tabel Kebenaran R-S flip-flop with active HIGH inputs

Prinsip kerja rangkain diatas ketika S berlogika 0 maka not nya berlogika 1 (a) dan berlogika 1 (b) maka output gerbang NAND akan berlogika 0 karena pada ujuang gerbang NAND terdapat not. ketika R berlogika 1 maka not nya berlogika 0 (a) dan berlogika 0 (b) maka output gerbang NAND akan berlogika 1 karena pada ujuang gerbang NAND terdapat not.

Berikut tabel kebenarannya:

3. NOR implementation of an R-S flip-flop.

Gambar (c) 10.19 NOR implementation of an R-S flip-flop.

Persamaan karakteristik untuk R-S flip-Flops dengan input tinggi aktif rendah dan aktif

diberikan oleh persamaan :

S + R = 1 menunjukkan bahwa R = S = 0 adalah entri yang dilarang. Demikian pula, SR = 0 hanya menunjukkan bahwa R = S = 1

adalah entri yang dilarang.

4. Clocked R-S flip-flop with active HIGH inputs

Gambar (d) 10.20 Clocked R-S flip-flop with active HIGH inputs.

Ketika sinyal clock tinggi, dua gerbang NAND diaktifkan dan input S dan R akan

diteruskan ke Flip-Flop input dengan status mereka dilengkapi. Output sekarang dapat mengubah status per

status R dan S pada input Flip-Flop. Misalnya, ketika S = 1 dan R = 0 itu akan diteruskan sebagai

0 dan 1 masing-masing ketika jam tinggi. Ketika jam rendah, dua gerbang NAND menghasilkan

' 1 ' pada output mereka, terlepas dari S dan R status. Ini menghasilkan logika ' 1 ' pada kedua input dari

Flip-Flop, dengan hasil bahwa tidak ada efek pada output.

Tabel Kebenaran Clocked R-S flip-flop with active HIGH inputs.

5. Clocked R-S flip-flop with active LOW inputs

Gambar (e) 10.21 Clocked R-S flip-flop with active LOW inputs.

Hampir sama dengan Clocked R-S flip-flop with active HIGH inputs. Hanya saja pada Clocked R-S flip-flop with active LOW inputs adanya tambahan logika NOT setelah keluaran dari kedua gerbang NAND pertama sebelum menuju kegerbang NAND berikutnya. Akibatnya nilainya akan dibalikkan oleh gerbang NOT apabila masukannya '1' maka dibalikkan menjadi '0' dan sebaliknya jika '0' maka dibalikkan oleh gerbang NOT menjadi '1'.

Tabel Kebenaran

a. Video Rangkaian gambar (a) 10.17 R-S Flip-Flop with Active LOW Inputs

b. Video Rangkaian gambar (b) 10.17 R-S Flip-Flop with Active HIGH Inputs

c. Video Rangkaian gambar (c) 10.19 NOR implementation of an R-S flip-flop

d. Video Rangkaian gambar (d) 10.20 Clocked R-S flip-flop with active HIGH inputs

e. VIdeo Rangkaian gambar (e) 10.21 Clocked R-S flip-flop with active LOW inputs

6. Link Download [Kembali]

File Rangkaian

Download Rangkaian gambar (a) 10.17 R-S Flip-Flop with Active LOW Inputs - disini

Download Rangkaian gambar (b) 10.17 R-S Flip-Flop with Active HIGH Inputs - disini

Download Rangkaian gambar (c) 10.19 NOR implementation of an R-S flip-flop - disini

Download Rangkaian gambar (d) 10.20 Clocked R-S flip-flop with active HIGH inputs - disini

Download Rangkaian gambar (e) 10.21 Clocked R-S flip-flop with active LOW inputs - disini

File Video

File Rangkaian

Download Rangkaian gambar (a) 10.17 R-S Flip-Flop with Active LOW Inputs - disini

Download Rangkaian gambar (b) 10.17 R-S Flip-Flop with Active HIGH Inputs - disini

Download Rangkaian gambar (c) 10.19 NOR implementation of an R-S flip-flop - disini

Download Rangkaian gambar (d) 10.20 Clocked R-S flip-flop with active HIGH inputs - disini

Download Rangkaian gambar (e) 10.21 Clocked R-S flip-flop with active LOW inputs - disini

File Video

Download Video Rangkaian gambar (a) 10.17 R-S Flip-Flop with Active LOW Inputs - disini

Download Video Rangkaian gambar (b) 10.17 R-S Flip-Flop with Active HIGH Inputs - disini

Download Video Rangkaian gambar (c) 10.19 NOR implementation of an R-S flip-flop - disini

Download Video Rangkaian gambar (d) 10.20 Clocked R-S flip-flop with active HIGH inputs - disini

Download VIdeo Rangkaian gambar (e) 10.21 Clocked R-S flip-flop with active LOW inputs - disini

Download Video Rangkaian gambar (b) 10.17 R-S Flip-Flop with Active HIGH Inputs - disini

Download Video Rangkaian gambar (c) 10.19 NOR implementation of an R-S flip-flop - disini

Download Video Rangkaian gambar (d) 10.20 Clocked R-S flip-flop with active HIGH inputs - disini

Download VIdeo Rangkaian gambar (e) 10.21 Clocked R-S flip-flop with active LOW inputs - disini

Tidak ada komentar:

Posting Komentar